# TMS7000 family

# Data Manual

# TMS7000 Family Data Manual

International Manual

### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Texas Instruments products are not intended for use in life-support appliances, devices, or systems. Use of a TI product in such applications without the written consent of the appropriate TI officer is prohibited.

### WARNING

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

# **Read This First**

This book replaces the following manuals:

- TMS7000 Family Data Manual, SPND001B

- TMS7000 Assembly Language Programmer's Guide, SPNU002B

- TMS7000 Software Development System Installation Guide, MPB52

- TMS7000 IBM CrossWare Support Reference Guide, MPB10

- TMS7000 VAX/VMS CrossWare Support Reference Guide, MPB53

The following table lists related publications.

| TMS7000 Data Sheets and Data Manuals                 | Literature Number |

|------------------------------------------------------|-------------------|

| TMS70C42/TMS70C02 Data Sheet                         | SPNS009           |

| TMS7000 User's Guides                                | Literature Number |

| 8051 - TMS7041 System Conversion User's Guide        | SPNU003           |

| TMS7500/TMS75C00 Data Encryption Device User's Guide | SPNU004           |

| Link Editor User's Guide                             | SPDU037C          |

| TMS7000 EVM User's Guide                             | SPNU007           |

| TMS7000 Family Development System Support            | Literature Number |

| XDS/22 with the TMS7042 Emulator Pocket Reference    | SPDF010           |

### How to Use This Manual

|           | This manual is divided into four major parts:                                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>□ Hardware (Chapters 2–4)</li> <li>□ Software (Chapters 5–8)</li> <li>□ Development Support (Chapters 9–10)</li> <li>□ Customer Information (Chapter 11)</li> </ul> |

|           | The chapters and their contents are summarized below.                                                                                                                        |

| Chapter 1 | Introduction                                                                                                                                                                 |

|           | Introduces the TMS7000 family devices.  Describes the different manual sections and their contents.                                                                          |

| Chapter 2 | TMS7000 Family Devices                                                                                                                                                       |

|           | Details each TMS7000 family category and their key features.                                                                                                                 |

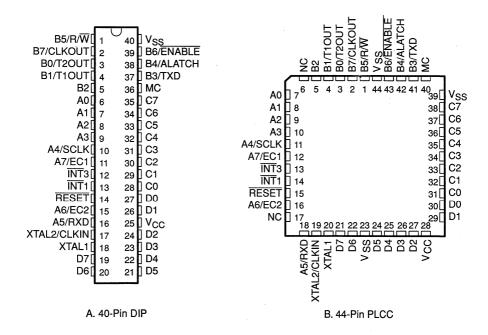

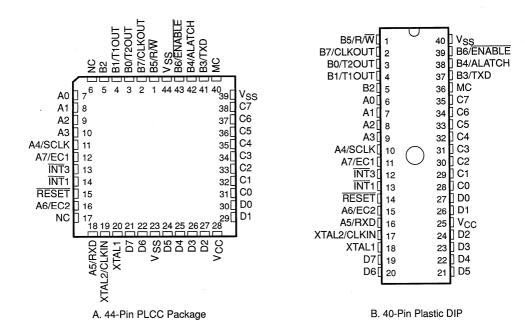

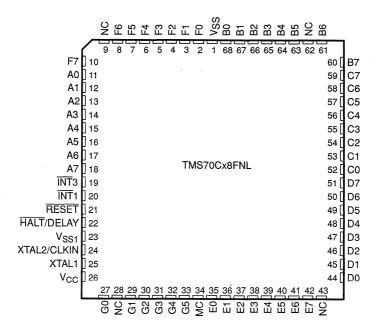

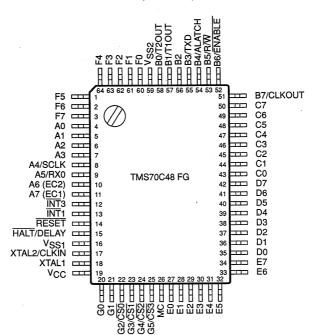

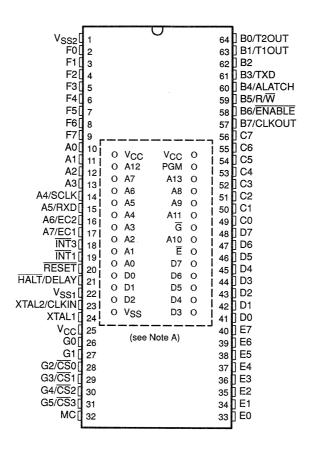

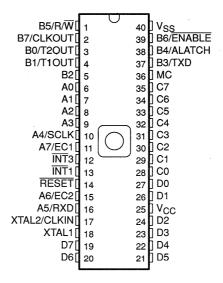

|           | Summarizes the categories and compares their features.  Provides key features, pinouts, and pin descriptions for each category of devices.                                                                                                                                                                      |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 3 | TMS7000 Family Architecture                                                                                                                                                                                                                                                                                     |

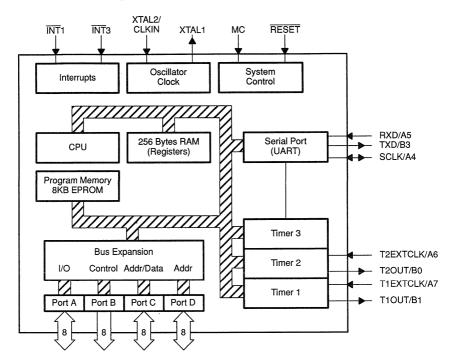

|           | Discusses operation of the microcomputers' hardware features Registers I/O Memory and memory modes Clock options CMOS low-power modes Interrupts Timer/event counters (TMS70Cx0 devices) Serial port (TMS70Cx2 devices only)                                                                                    |

| Chapter 4 | Electrical Specifications                                                                                                                                                                                                                                                                                       |

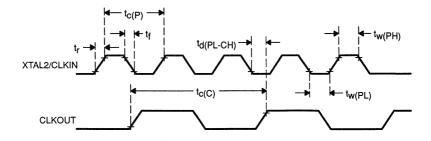

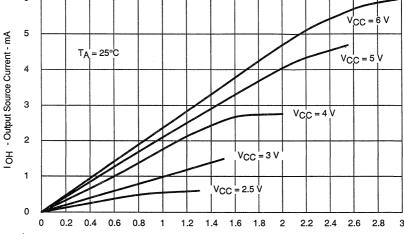

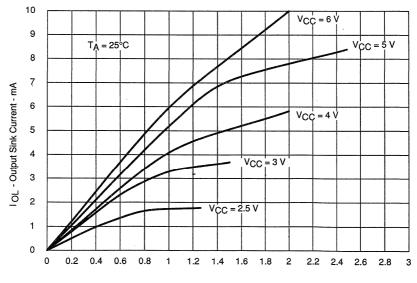

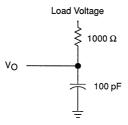

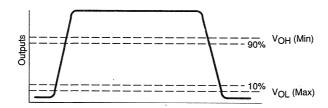

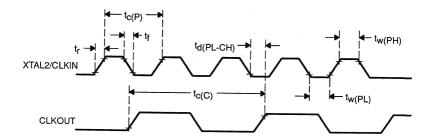

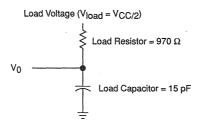

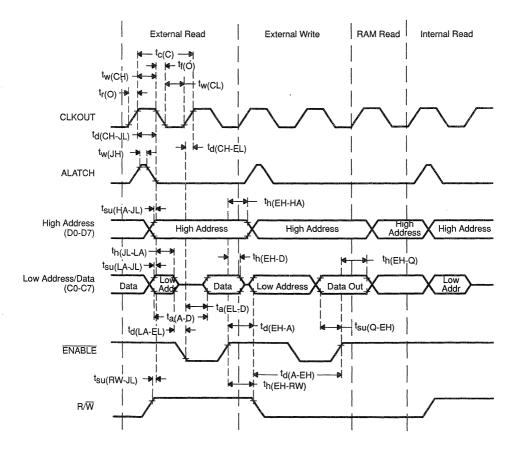

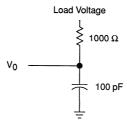

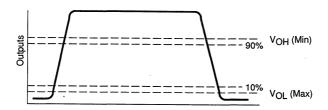

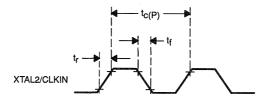

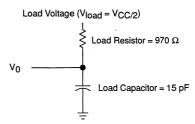

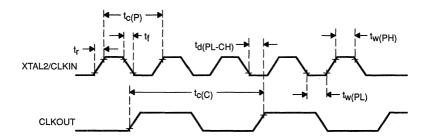

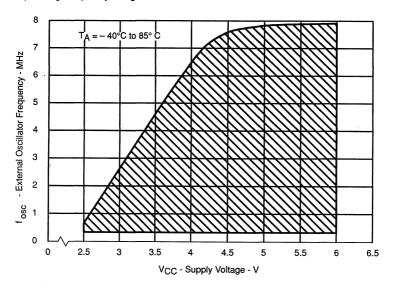

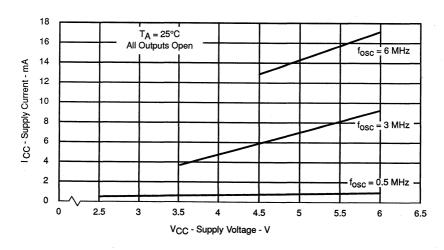

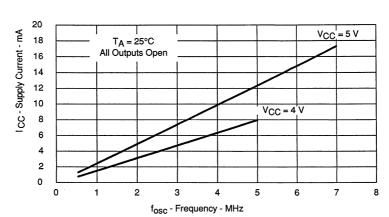

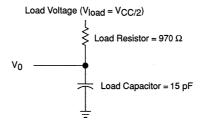

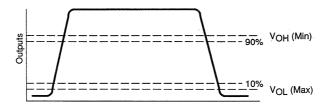

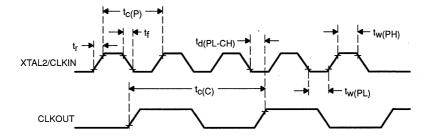

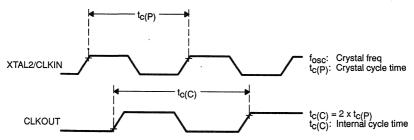

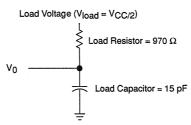

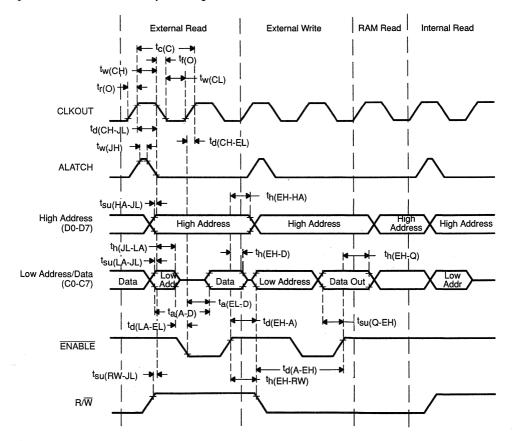

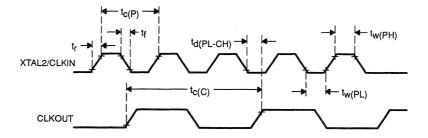

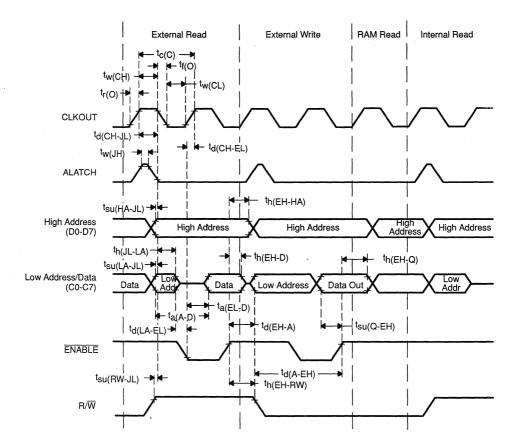

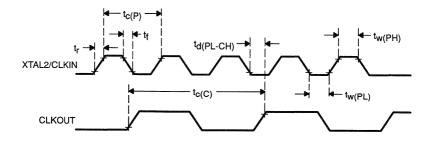

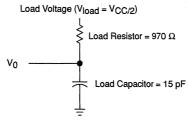

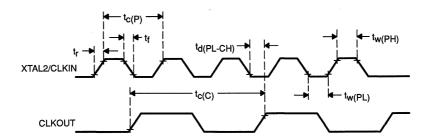

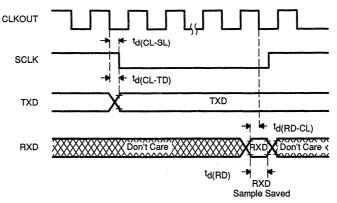

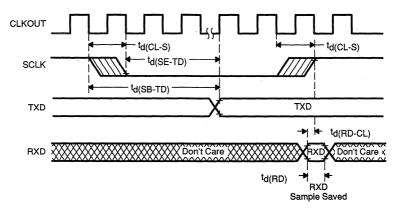

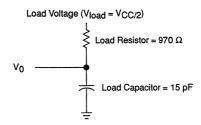

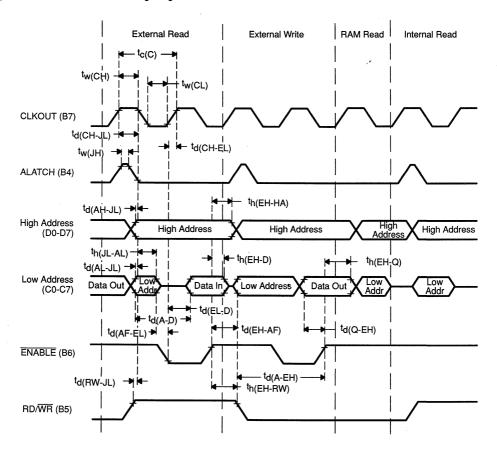

|           | Discusses for all device groups:  Absolute maximum ratings  Recommended operating characteristics  Recommended crystal/clockin operating characteristics  Memory interface timing  Read and write cycle timing  Ceramic resonator circuit application (where applicable)  Serial port timing (where applicable) |

| Chapter 5 | TMS7000 Assembler                                                                                                                                                                                                                                                                                               |

|           | Discusses basic assembler information, including:  Source statement format (placement of various fields in code)  Constants, symbols, terms, and expressions                                                                                                                                                    |

|           | <ul> <li>Discusses the various assembler directives, grouped in the following categories:</li> <li>Directives that affect the location counter</li> <li>Directives that affect assembler output</li> <li>Directives that initialize constants</li> </ul>                                                        |

|           |           | <ul> <li>Explains source listing format and resulting object code.</li> <li>Presents normal completion and abnormal completion error messages.</li> <li>Shows a sample cross reference listing.</li> <li>Discusses object code and the various fields in object code format, and changing object code.</li> <li>Shows assembling file examples.</li> </ul> |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 6 | Ass       | sembly Language Instruction Set                                                                                                                                                                                                                                                                                                                            |

|           |           | Provides general instruction set information, such as symbol definitions. Defines eight addressing modes used by the instructions.  Summarizes the instruction set in table form.  Presents the TMS7000 assembly language instruction set in alphabetical order.                                                                                           |

| Chapter 7 | Lin       | king Program Modules                                                                                                                                                                                                                                                                                                                                       |

|           |           | Discusses relocation capability, absolute and relocatable code. Discusses the Link Editor and includes a sample link control file. Reviews directives needed for linking programs.                                                                                                                                                                         |

| Chapter 8 | Ma        | cro Language                                                                                                                                                                                                                                                                                                                                               |

|           | _         |                                                                                                                                                                                                                                                                                                                                                            |

| Chapter 9 |           | sign Aids<br>cludes several examples to help you use the TMS7000 family devices:                                                                                                                                                                                                                                                                           |

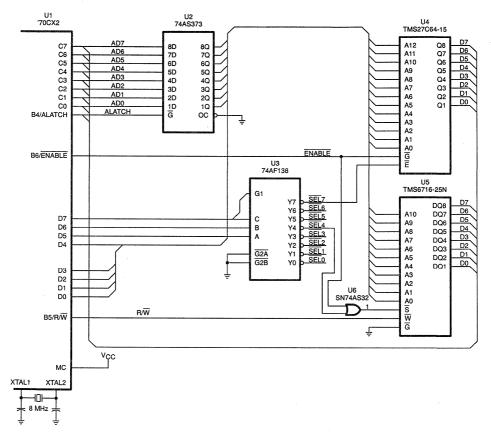

|           | 0 0000000 | Interfacing the TMS7000 to peripheral and memory devices such as extra EPROM and RAM Programming the TMS77C82 Serial communication using the UART (serial port) Instruction set application notes Sample routines The status register Stack operations Multiplication and shifting                                                                         |

Directives for linking programs Miscellaneous directives

Assembler Output

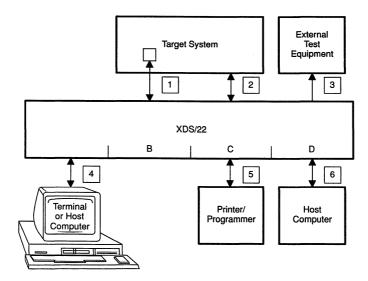

| Chapter 10 | <ul> <li>□ The branch instruction</li> <li>□ Interrupts</li> <li>□ Write-Only registers</li> <li>Development Support</li> <li>Discusses several products manufactured by Texas Instruments that enhance</li> <li>TMS77000 family design development, including:</li> <li>□ TMS77C82 Starter Kit</li> <li>□ XDS (Extended Development Support) Emulator</li> <li>□ EVM (evaluation module)</li> <li>□ Prototyping devices</li> </ul>         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

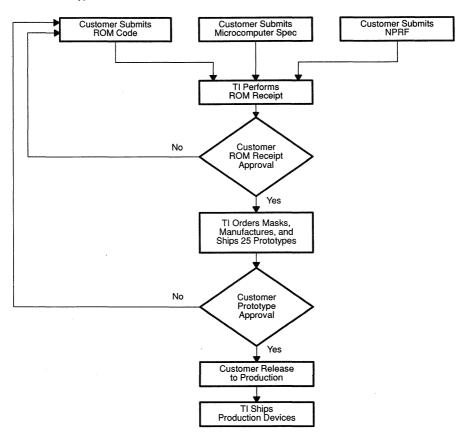

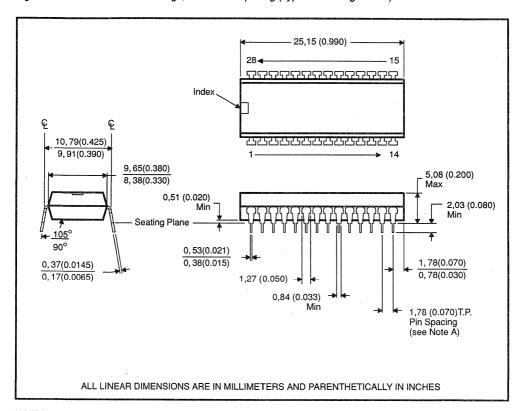

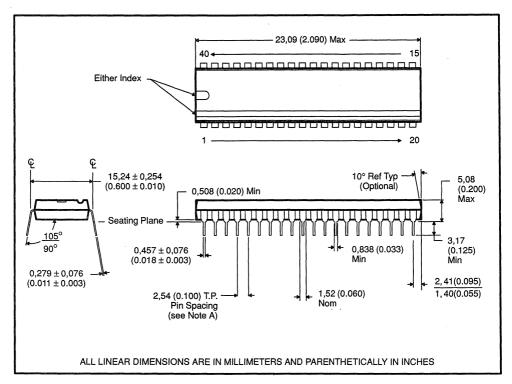

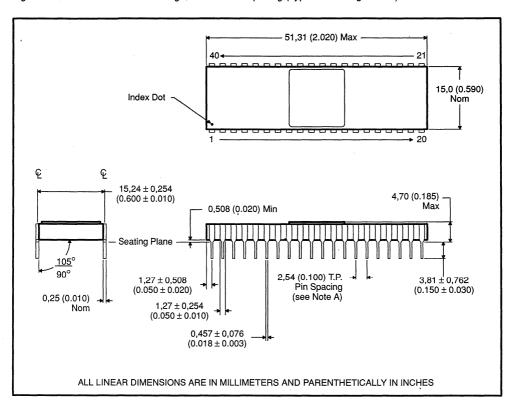

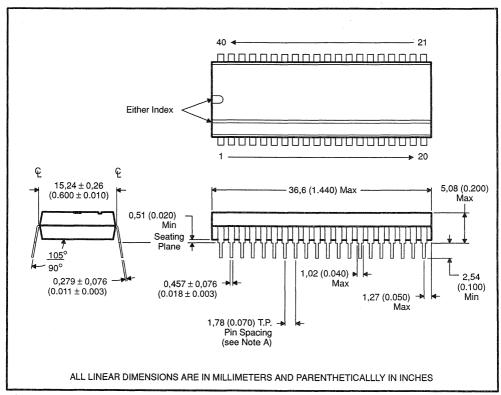

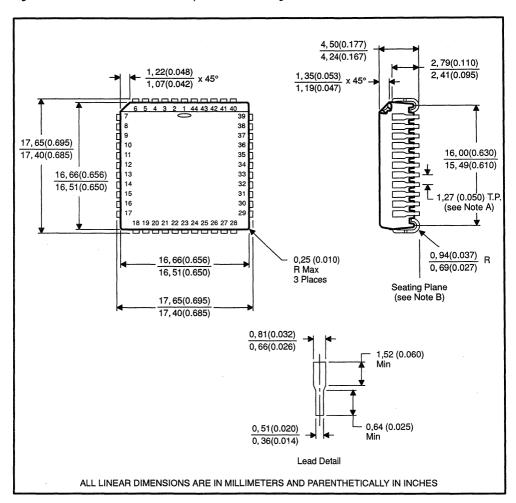

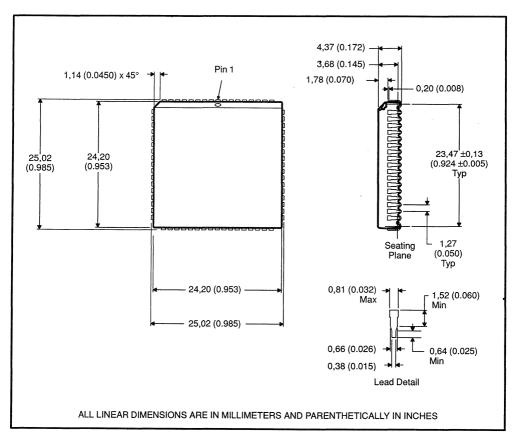

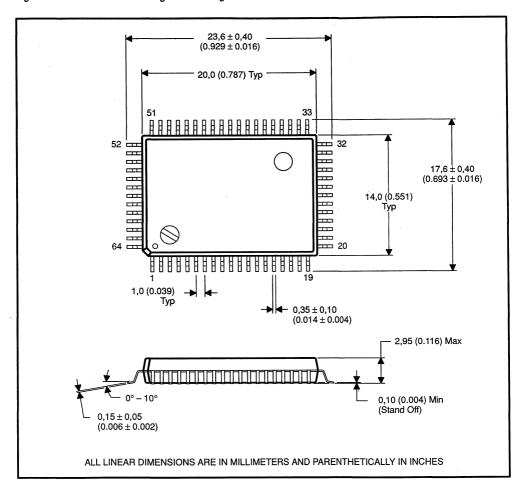

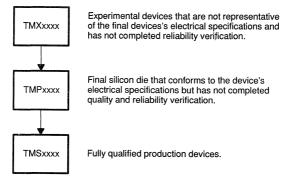

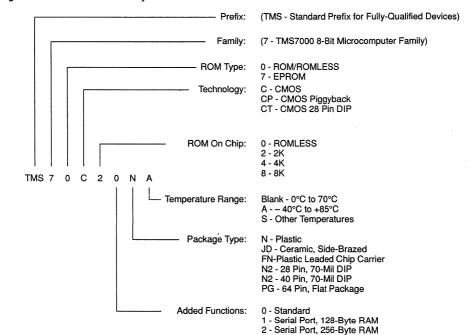

| Chapter 11 | Customer Information  □ Discusses quality and reliability. □ Discusses prototype manufacture and production flow, including device prefix designators – TMS, TMP, TMX, and SE. □ Illustrates mechanical package information for all TMS7000 family members □ Provides ordering information for the TMS7000 microcomputers and the Texas Instruments development support products. □ Adaptors and hardware □ Application Boards and Packages |

| Appendix A | TMS7000 Bus Activity Tables                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Appendix B | TMS7000 NMOS to CMOS Conversion Guide                                                                                                                                                                                                                                                                                                                                                                                                       |

| Appendix C | Character Sets                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Appendix D | Hexadecimal Instruction Table/Opcode Map                                                                                                                                                                                                                                                                                                                                                                                                    |

| Appendix E | Instruction Opcode Set                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Appendix F | Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Index      |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## Related Documentation

Communication Equipment Employing Serial Binary Data Interchange, Engineering Department, Electronic Industries Association, 2001 Eye Street, N.W., Washington D.C. 20006, August 1969.

vı Read This First

### Information about Cautions and Warnings

This book may contain cautions and warnings.

A caution describes a situation that could potentially damage your software or equipment.

A warning describes a situation that could potentially cause harm to you.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

### Trademarks

CodeView, MS-Windows, MS, and MS-DOS are trademarks of Microsoft Corp. DEC, Digital DX, VAX, VMS, and Ultrix are trademarks of Digital Equipment Corp. EPIC, XDS, TIGA, and TIGA-340 are trademarks of Texas Instruments, Inc. PC-DOS. PGA, and Micro Channel are trademarks of IBM Corp.

VIII Read This First

# **Contents**

| 1 | Intro | duction  |                                                               | 1-1 |

|---|-------|----------|---------------------------------------------------------------|-----|

|   | 1.1   | Update   | s Added to This Manual 1                                      | 1-4 |

| 2 | TMS7  | 7000 Fan | nily Devices                                                  | 2-1 |

|   | 2.1   |          | ary and Device Comparison                                     |     |

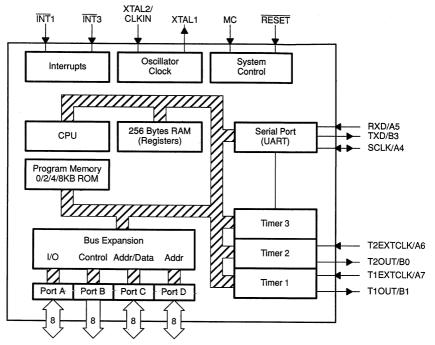

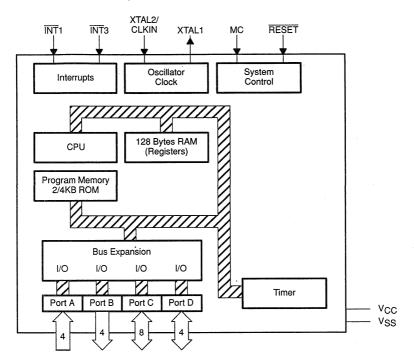

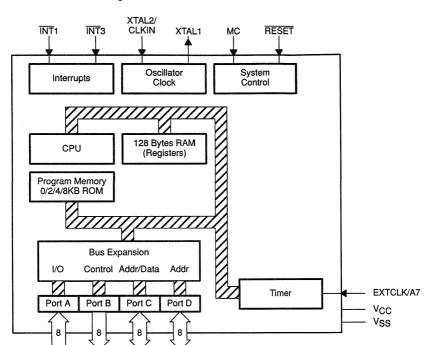

|   | 2.2   |          | Cx0 and TMS70CTx0 Key Features                                |     |

|   |       | 2.2.1    | TMS70CTx0 Key Features                                        |     |

|   |       | 2.2.2    | TMS70Cx0 Key Features                                         | 2-6 |

|   | 2.3   | TMS70    | Cx2 Devices                                                   | -10 |

|   | 2.4   | TMS70    | Cx8 Devices                                                   | -13 |

|   |       | 2.4.1    | TMS70Cx8 Key Features 2-                                      | -13 |

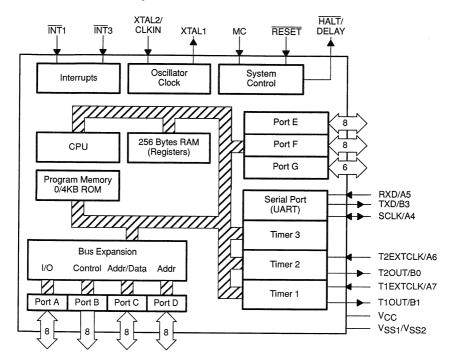

|   | 2.5   | SE70C    | P160, TMS77C82, and SE70CP168 Prototyping Devices 2-          | -18 |

|   |       | 2.5.1    | SE70CP160 (CMOS) Piggyback Prototyping Device Key Features 2- | -18 |

|   |       | 2.5.2    | SE70CP168 Piggyback Prototyping Device Key Features 2-        |     |

|   |       | 2.5.3    | TMP77C82 JDL CMOS EPROM Prototyping Device Key Features 2-    | -22 |

| 3 | TMS7  | 7000 Fan | nily Architecture                                             | 3-1 |

|   | 3.1   | On-Chi   | p RAM and Registers                                           | 3-7 |

|   |       | 3.1.1    | Register File (RF)                                            |     |

|   |       | 3.1.2    | Peripheral File (PF)                                          |     |

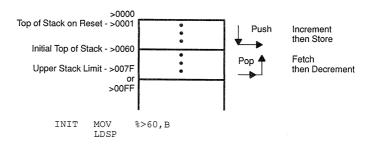

|   |       | 3.1.3    | Stack Pointer (SP)                                            |     |

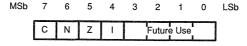

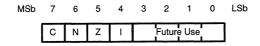

|   |       | 3.1.4    | Status Register (ST)                                          |     |

|   |       | 3.1.5    | Program Counter (PC)                                          |     |

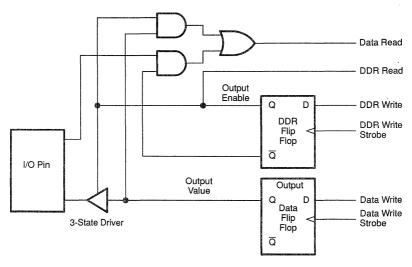

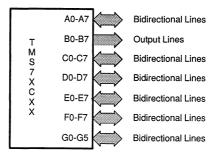

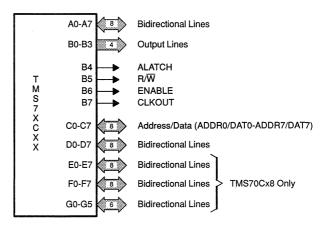

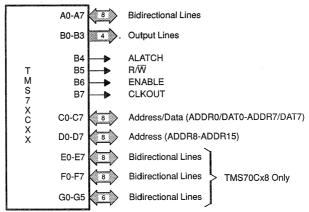

|   | 3.2   | On-Chi   | p General Purpose I/O Ports                                   |     |

|   |       | 3.2.1    |                                                               | -14 |

|   |       | 3.2.2    | Port B 3-                                                     | -14 |

|   |       | 3.2.3    | Port C 3-                                                     | -15 |

|   |       | 3.2.4    | Port D 3-                                                     | -15 |

|   |       | 3.2.5    | Ports E and F 3-                                              | -15 |

|   |       | 3.2.6    | Port G 3-                                                     | -15 |

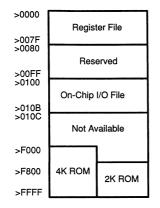

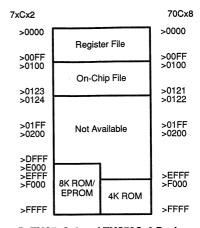

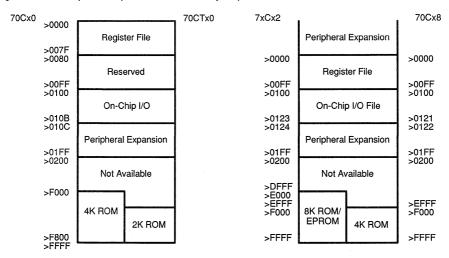

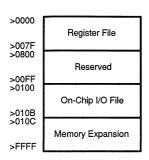

|   | 3.3   | Memor    | y Modes 3-                                                    | -16 |

|   |       | 3.3.1    | Single-Chip Mode 3-                                           | -22 |

|   |       | 3.3.2    | Peripheral-Expansion Mode 3-                                  |     |

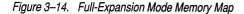

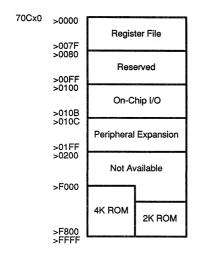

|   |       | 3.3.3    | Full-Expansion Mode 3-                                        |     |

|   |       | 3.3.4    | Microprocessor Mode 3-                                        |     |

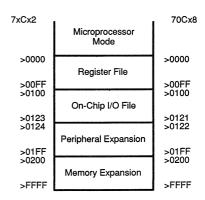

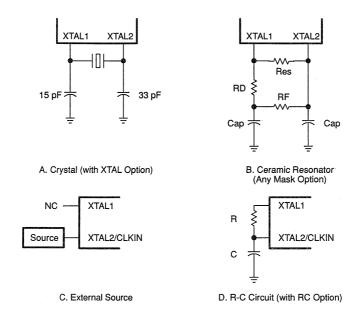

|   | 3.4   | System   | Clock Options                                                 |     |

Х

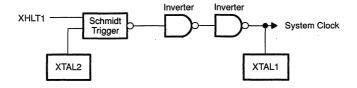

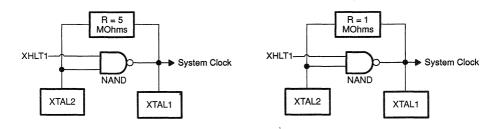

|   |        | 3.4.1     | System Clock Connections                                                                      | . 3-31 |

|---|--------|-----------|-----------------------------------------------------------------------------------------------|--------|

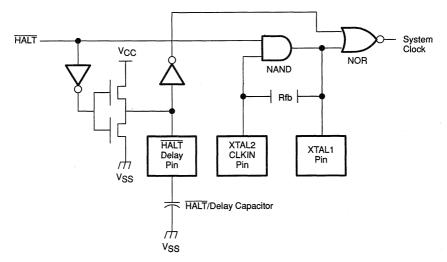

|   |        | 3.4.2     | Low-Power Mask Option                                                                         | . 3-33 |

|   | 3.5    | Low-Po    | ower Modes                                                                                    | . 3-36 |

|   |        | 3.5.1     | TMS70Cx0 and TMS70CTx0 Low-Power Modes                                                        | . 3-36 |

|   |        | 3.5.2     | TMS70Cx2 Devices                                                                              | . 3-37 |

|   |        | 3.5.3     | TMS70Cx8 Devices                                                                              |        |

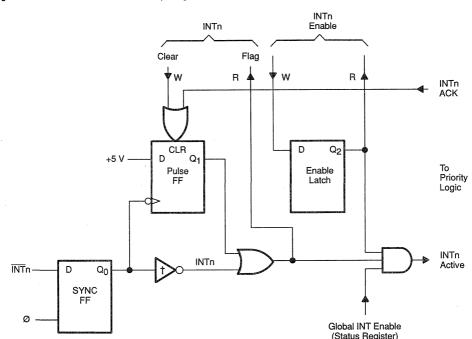

|   | 3.6    | Interrup  | pts and System Reset                                                                          |        |

|   |        | 3.6.1     | Device Initialization                                                                         |        |

|   |        | 3.6.2     | Interrupt Operation                                                                           |        |

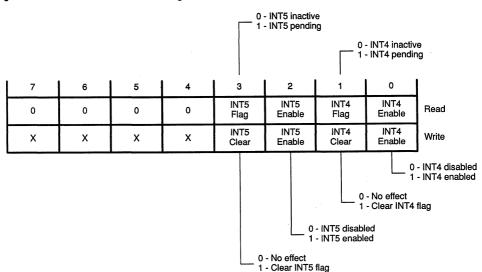

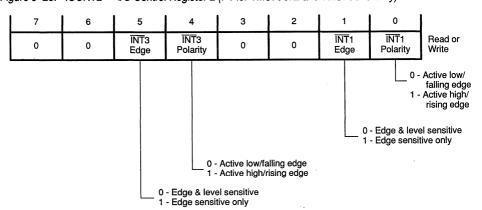

|   |        | 3.6.3     | Interrupt Control                                                                             |        |

|   |        | 3.6.4     | Multiple Interrupt Servicing                                                                  |        |

|   |        | 3.6.5     | External Interrupt Servicing                                                                  |        |

|   |        | 3.6.6     | External Interrupt Signals                                                                    |        |

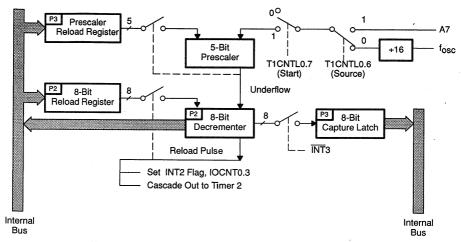

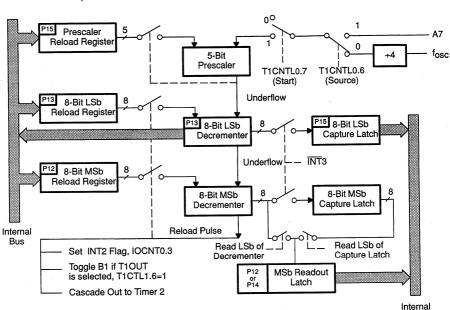

|   | 3.7    | _         | mmable Timer/Event Counters                                                                   | . 3-53 |

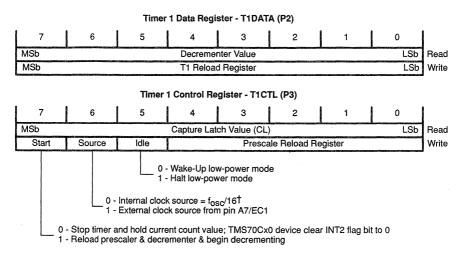

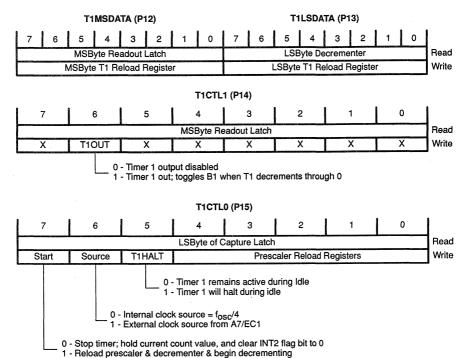

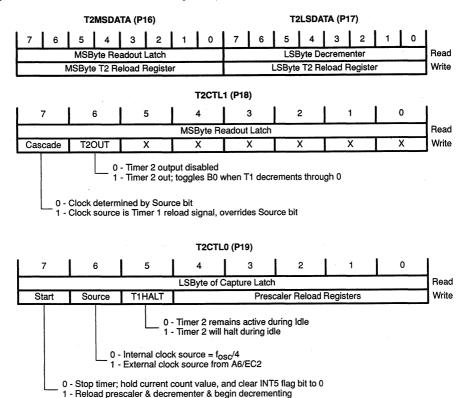

|   |        | 3.7.1     | Control Registers for Timer/Event Counters 1 and 2 (TMS70Cx0 and TMS70CTx0 Devices)           | . 3-60 |

|   |        | 3.7.2     | Control Registers for Timer/Event Counters 1 and 2 (TMS70Cx2, TMS77C82, and TMS70Cx8 Devices) | . 3-60 |

|   |        | 3.7.3     | Timer Start/Stop (Bit 7) and Capture Latch                                                    | . 3-61 |

|   |        | 3.7.4     | Clock Source Control (Bit 6) (See note below.)                                                |        |

|   |        | 3.7.5     | Idle/Timer Halt Bit (Bit 5)                                                                   |        |

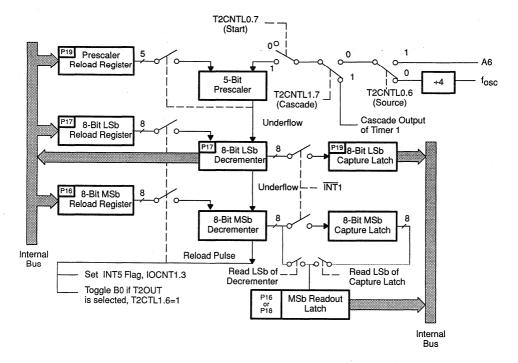

|   |        | 3.7.6     | Cascading Timers                                                                              |        |

|   |        | 3.7.7     | Timer and Prescaler Operation                                                                 | . 3-64 |

|   |        | 3.7.8     | Timer Interrupts                                                                              | . 3-66 |

|   |        | 3.7.9     | Pulse Width Modulation, Timer Output Function (TMS70Cx2, TMS77C82, and TMS70Cx8)              | . 3-67 |

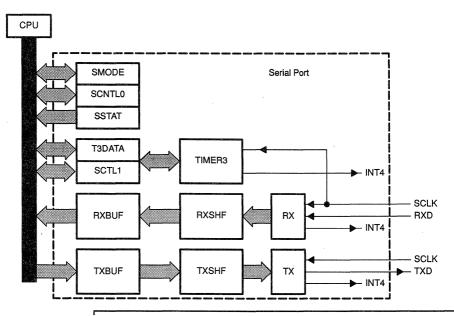

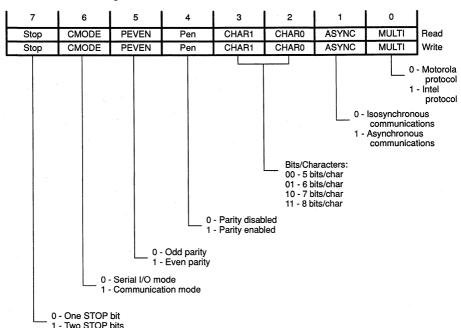

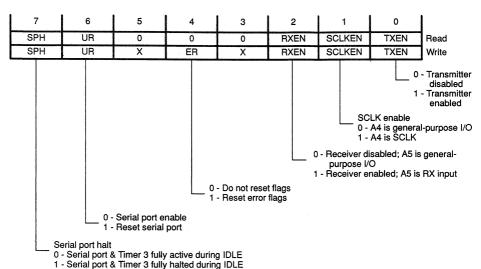

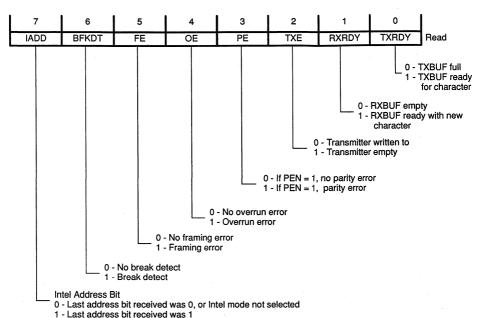

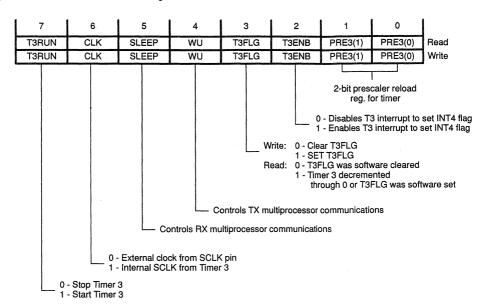

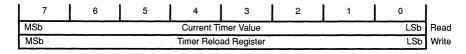

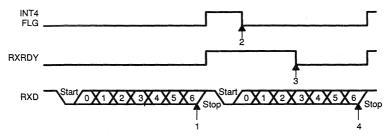

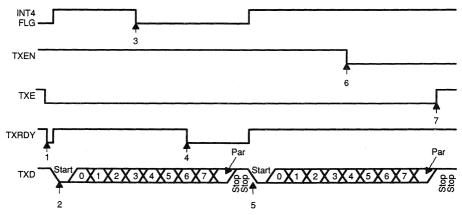

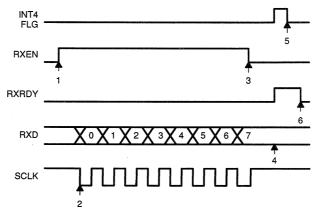

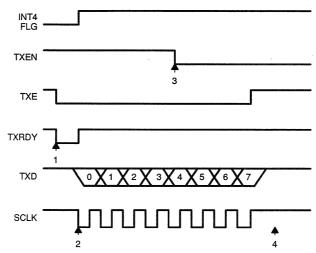

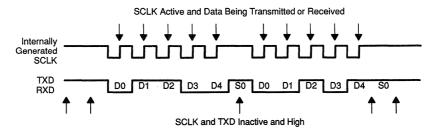

|   | 3.8    | Serial F  | Port (TMS70Cx2, TMS77C82, and TMS70Cx8 Devices Only)                                          | . 3-68 |

|   |        | 3.8.1     | Serial Port Registers                                                                         |        |

|   |        | 3.8.2     | Serial Port Clock Sources                                                                     |        |

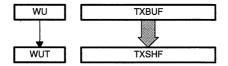

|   |        | 3.8.3     | Multiprocessor Communication                                                                  |        |

|   |        | 3.8.4     | Serial Port Initialization                                                                    |        |

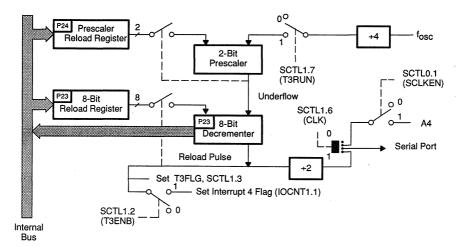

|   |        | 3.8.5     | Timer 3                                                                                       |        |

|   |        | 3.8.6     | Initialization Examples                                                                       |        |

|   |        | 3.8.7     | Serial Port Interrupts                                                                        | . 3-95 |

| 1 | Electi | rical Spe | ecifications                                                                                  | 4.1    |

|   | 4.1    |           | C00, TMS70C20, and TMS70C40 Specifications (Wide Voltage)                                     |        |

|   | 4.2    | TMS70     | C00, TMS70C20, and TMS70C40 Specifications (5V +10%)                                          | . 4-10 |

|   | 4.3    | TMS70     | CT20 and TMS70CT40 Specifications (5 V + 10%)                                                 | . 4-17 |

|   | 4.4    |           | C02, TMS70C42, and TMS70C82 Specifications (Wide Voltage)                                     |        |

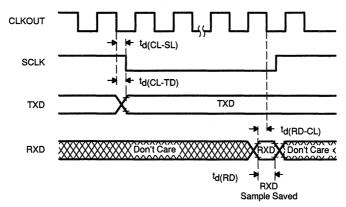

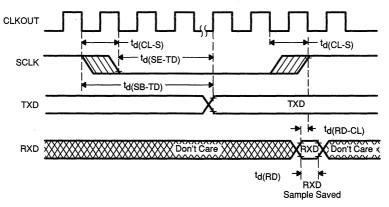

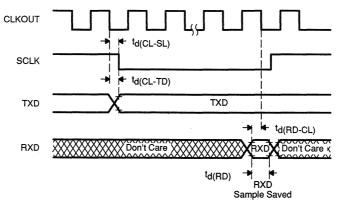

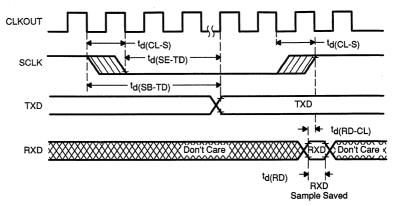

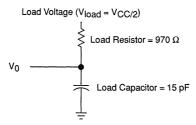

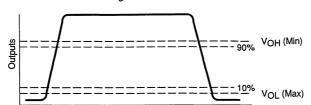

|   |        | 4.4.1     | Serial Port Timing                                                                            |        |

|   | 4.5    | TMS70     | C02, TMS70C42, and TMS70C82 Specifications (5V +10%)                                          |        |

|   |        | 4.5.1     | Serial Port Timing                                                                            |        |

|   | 4.6    | TMS70     | C08 and TMS70C48 Specifications                                                               |        |

|   | 4.7    |           | P160A Specifications                                                                          |        |

|   |        |           |                                                                                               | /      |

Table of Contents

|   | 4.8   |        | 7C82 Specifications                         |     |

|---|-------|--------|---------------------------------------------|-----|

|   | 4.0   | 4.8.1  | Serial Port Timing                          |     |

|   | 4.9   |        | P168 Specifications                         | -59 |

| 5 | The T | MS7000 | O Assembler                                 | 5-1 |

|   | 5.1   | Source | Statement Format                            | 5-2 |

|   |       | 5.1.1  | Label Field                                 | 5-5 |

|   |       | 5.1.2  | Command Field                               | 5-5 |

|   |       | 5.1.3  | Operand Field                               | 5-5 |

|   |       | 5.1.4  | Comment Field                               | 5-5 |

|   | 5.2   | Consta | ints                                        | 5-6 |

|   |       | 5.2.1  | Decimal Integer Constants                   | 5-6 |

|   |       | 5.2.2  | Binary Integer Constants                    | 5-6 |

|   |       | 5.2.3  | Hexadecimal Integer Constants               | 5-6 |

|   |       | 5.2.4  | Character Constants                         | 5-7 |

|   |       | 5.2.5  | Assembly-Time Constants                     | 5-7 |

|   | 5.3   | Symbo  | ls                                          | 5-8 |

|   |       | 5.3.1  | Predefined Symbols                          | 5-8 |

|   |       | 5.3.2  | Terms                                       | 5-8 |

|   |       | 5.3.3  | Character Strings                           | 5-9 |

|   | 5.4   | Expres | sions 5                                     | -10 |

|   |       | 5.4.1  | Arithmetic Operators in Expressions 5       | -10 |

|   |       | 5.4.2  | Logical Operands in Expressions 5           | -11 |

|   |       | 5.4.3  | Parentheses in Expressions 5                |     |

|   |       | 5.4.4  | Well-Defined Expressions                    |     |

|   |       | 5.4.5  | Relocatable Symbols in Expressions          |     |

|   |       | 5.4.6  | Externally Defined Symbols in Expressions 5 |     |

|   | 5.5   | Assem  | bler Directives 5                           |     |

|   | 5.6   |        | lic Addressing Techniques 5                 |     |

|   | 5.7   |        | bler Output 5                               |     |

|   |       | 5.7.1  | Source Listing 5                            |     |

|   |       | 5.7.2  | Normal Completion Error Messages            |     |

|   |       | 5.7.3  | Abnormal Completion Error Messages          |     |

|   |       | 5.7.4  | Cross-Reference Listing                     |     |

|   | 5.8   | Object | Code 5                                      |     |

|   |       | 5.8.1  | Object Code Format                          |     |

|   | 5.9   | Assem  | bling Files – Examples                      |     |

| _ |       |        |                                             |     |

| 6 |       | -      | Inguage Instruction Set                     |     |

|   | 6.1   |        | ons                                         |     |

|   | 6.2   |        | sing Modes                                  |     |

|   |       | 6.2.1  | Single Register Addressing Mode             |     |

|   |       | 6.2.2  | Dual Register Addressing Mode               |     |

|   |       | 6.2.3  | Peripheral-File Addressing Mode             | 6-4 |

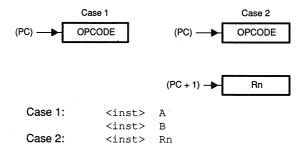

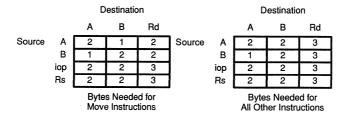

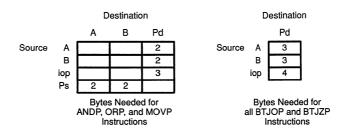

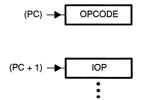

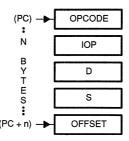

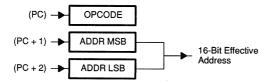

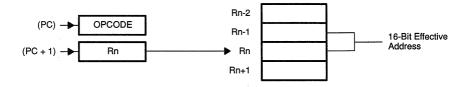

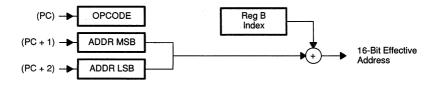

| 6.2.7 Register File Indirect Addressing Mode 6.2.8 Indexed Addressing Mode 6.3 Instruction Set Overview 6.4 Software Compatibility 6.4.1 TMS70C42 and TMS70C82 Directly Compatible 6.4.2 TMS70C20, TMS70C40, TMS70CT20, TMS70CT40  7 Linking Program Modules 7.1 Relocation Capability 7.2 Link Editor Operation 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files – Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters                                                                                                                                                                                                                                                                                                                                                 |   |        | 6.2.4<br>6.2.5<br>6.2.6 | Immediate Addressing Mode                  | 6-5  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|-------------------------|--------------------------------------------|------|

| 6.2.8 Indexed Addressing Mode 6.3 Instruction Set Overview 6.4 Software Compatibility 6.4.1 TMS70C42 and TMS70C82 Directly Compatible 6.4.2 TMS70C20, TMS70C40, TMS70CT20, TMS70CT40  7 Linking Program Modules 7.1 Relocation Capability 7.2 Link Editor Operation 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files — Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4.1 Symbol Components 8.4.2 Parameter Attribute Keywords 8.4.1 Symbol Attribute Component Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages |   |        |                         |                                            |      |

| 6.3 Instruction Set Overview 6.4 Software Compatibility 6.4.1 TMS70C42 and TMS70C82 Directly Compatible 6.4.2 TMS70C20, TMS70C40, TMS70CT20, TMS70CT40  7 Linking Program Modules 7.1 Relocation Capability 7.2 Link Editor Operation 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files — Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                          |   |        |                         |                                            |      |

| 6.4 Software Compatibility 6.4.1 TMS70C42 and TMS70C82 Directly Compatible 6.4.2 TMS70C20, TMS70C40, TMS70CT20, TMS70CT40  7 Linking Program Modules 7.1 Relocation Capability 7.2 Link Editor Operation 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files – Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries on MS/PC-DOS Systems 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.3.4 Symbol Components 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                       |   | 63     |                         |                                            |      |

| 6.4.1 TMS70C42 and TMS70C82 Directly Compatible 6.4.2 TMS70C20, TMS70C40, TMS70CT20, TMS70CT40  7 Linking Program Modules 7.1 Relocation Capability 7.2 Link Editor Operation 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files – Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries on MS/PC-DOS Systems 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                          |   |        |                         |                                            |      |

| 6.4.2 TMS70C20, TMS70C40, TMS70CT20, TMS70CT40  7 Linking Program Modules 7.1 Relocation Capability 7.2 Link Editor Operation 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files – Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                  |   | 0.4    |                         |                                            |      |

| 7. Linking Program Modules 7.1 Relocation Capability 7.2 Link Editor Operation 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files – Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.4.2 Parameter Attribute Keywords 8.4.3 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                               |   |        |                         |                                            |      |

| 7.1 Relocation Capability 7.2 Link Editor Operation 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files – Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                       |   |        | 6.4.2                   | TMS/0C20, TMS/0C40, TMS/0C120, TMS/0C140   | 6-/1 |

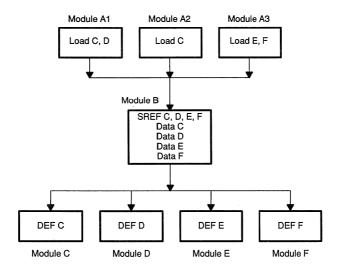

| 7.1 Relocation Capability 7.2 Link Editor Operation 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files – Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                       | 7 | Linkir | ng Prog                 | ram Modules                                | 7-1  |

| 7.2 Link Editor Operation 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files – Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4.4 Symbol Components 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro FILSE 8.9 Macro Error Messages  9 Design Aids                                                                                                                                                                                                                                                                                                                                             |   |        |                         |                                            |      |

| 7.3 Directives Used for Linking 7.4 Creating Linkable Files 7.5 Linking Files – Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                             |   | 7.2    |                         |                                            |      |

| 7.4 Creating Linkable Files 7.5 Linking Files – Examples  8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro FULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                |   | 7.3    |                         |                                            |      |

| 8 Macro Language 8.1 Defining Macros 8.1.1 Using Macro Libraries 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.3 Macro FACT 8.8.4 Macro Error Messages  9 Design Aids                                                                                                                                                                                                                                                                                                                                                                             |   | 7.4    |                         |                                            |      |

| 8.1 Defining Macros 8.1.1 Using Macro Libraries 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.3 Macro FACT 8.8.4 Macro Error Messages  9 Design Aids                                                                                                                                                                                                                                                                                                                                                                                              |   | 7.5    |                         | ·                                          |      |

| 8.1 Defining Macro Libraries 8.1.1 Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |        | _                       |                                            |      |

| 8.1.1 Using Macro Libraries 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3 | Macro  | <b>Langu</b>            | ıage                                       | 8-1  |

| 8.1.1.1Using Macro Libraries on MS/PC-DOS Systems 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 8.1    | Definin                 | g Macros                                   | 8-2  |

| 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |        | 8.1.1                   | Using Macro Libraries                      | 8-2  |

| 8.1.2 Sample Macros 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |        | 8.1.1.1                 | Using Macro Libraries on MS/PC-DOS Systems | 8-4  |

| 8.2 Strings, Constants, and Operators 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |        |                         | Sample Macros                              |      |

| 8.3 Variables 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 8.2    | Strings                 |                                            |      |

| 8.3.1 Parameters 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 | 8.3    |                         |                                            |      |

| 8.3.2 Macro Variable Components 8.3.3 Variable Qualifiers 8.3.4 Symbol Components 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |        |                         | Parameters                                 |      |

| 8.3.3 Variable Qualifiers 8.3.4 Symbol Components  8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |        | 8.3.2                   | Macro Variable Components                  |      |

| 8.3.4 Symbol Components  8.4 Keywords  8.4.1 Symbol Attribute Component Keywords  8.4.2 Parameter Attribute Keywords  8.5 Assigning Values to Parameters  8.6 Verbs  8.7 Model Statements  8.8 Macro Examples  8.8.1 Macro ID  8.8.2 Macro GENCMT  8.8.3 Macro FACT  8.8.4 Macro PULSE  8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |        |                         |                                            |      |

| 8.4 Keywords 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |        | 8.3.4                   |                                            |      |

| 8.4.1 Symbol Attribute Component Keywords 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 8.4    |                         |                                            |      |

| 8.4.2 Parameter Attribute Keywords 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |        |                         |                                            |      |

| 8.5 Assigning Values to Parameters 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages  9 Design Aids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |        | 8.4.2                   |                                            |      |

| 8.6 Verbs 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 8.5    |                         |                                            |      |

| 8.7 Model Statements 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages  9 Design Aids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |        |                         |                                            |      |

| 8.8 Macro Examples 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages  9 Design Aids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |        |                         |                                            |      |

| 8.8.1 Macro ID 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages  9 Design Aids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |        |                         |                                            |      |

| 8.8.2 Macro GENCMT 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages  9 Design Aids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 0.0    |                         |                                            |      |

| 8.8.3 Macro FACT 8.8.4 Macro PULSE 8.9 Macro Error Messages  9 Design Aids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |        |                         |                                            |      |

| 8.8.4 Macro PULSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |        |                         |                                            |      |

| 8.9 Macro Error Messages  9 Design Aids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |        |                         |                                            |      |

| 9 Design Aids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 8 Q    |                         |                                            |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | 0.5    | iviacio                 | LITUI Wessages                             | 8-32 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | - | Desia  | n Aids                  |                                            | 9_1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |        |                         |                                            |      |

| 9.1.1 Read Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |        |                         | Read Cycle Timing                          |      |

Table of Contents

|    |       | 9.1.2    | Write Cycle Timing for Microprocessor Mode                   | 9-5  |

|----|-------|----------|--------------------------------------------------------------|------|

|    | 9.2   | Progran  | nming the TMS77C82                                           | 9-6  |

|    |       | 9.2.1    | Programming the TMS77C82 Using an EPROM Programmer           | 9-6  |

|    |       | 9.2.2    | EPROM Integrity Protection Using the R Bit                   |      |

|    |       | 9.2.3    | Programming the TMS77C82 Using the TMS7000 Evaluation Module | 9-9  |

|    |       | 9.2.4    | Modify the BTC/EVM7000C Debug Monitor to Enable 12.5 Volt    |      |

|    |       |          | VPP Programming                                              | 9-10 |

|    |       | 9.2.5    | TMS77C82JDL Erasure                                          |      |

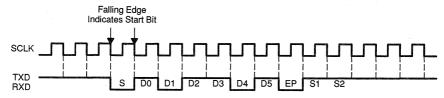

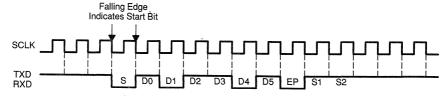

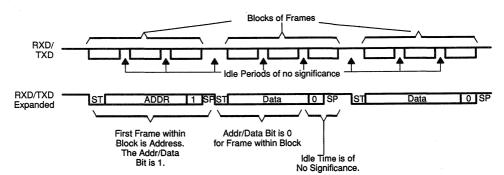

|    | 9.3   | Serial C | Communication with the TMS7000 Family                        | 9-12 |

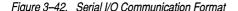

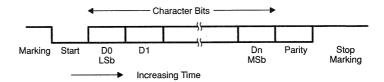

|    |       | 9.3.1    | Communication Formats                                        | 9-12 |

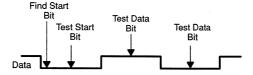

|    |       | 9.3.2    | Software UART (All TMS7000 Devices)                          | 9-13 |

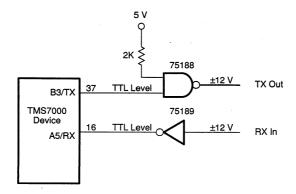

|    |       | 9.3.3    | Hardware UART (TMS7xCx2)                                     | 9-19 |

|    | 9.4   | The Sta  | ttus Register                                                | 9-24 |

|    |       | 9.4.1    | Compare and Jump Instructions                                | 9-24 |

|    |       | 9.4.2    | Addition and Subtraction Instructions                        |      |

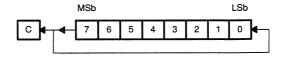

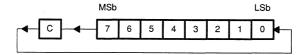

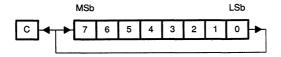

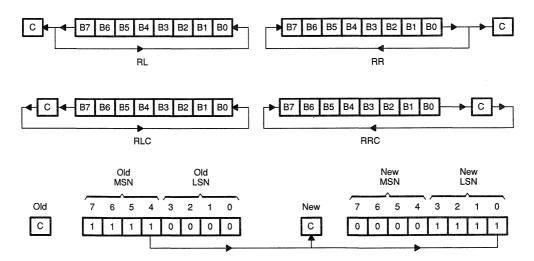

|    |       | 9.4.3    | Swap and Rotation Instructions                               | 9-26 |

|    | 9.5   | Stack C  | perations                                                    | 9-27 |

|    | 9.6   |          | tine Instructions                                            |      |

|    | 9.7   |          | cation and Shifting                                          |      |

|    | 9.8   | The Bra  | anch Instruction                                             | 9-31 |

|    | 9.9   |          | ts                                                           |      |

|    | 9.10  |          | nly Registers                                                |      |

|    | 9.11  | Sample   | Routines                                                     | 9-35 |

|    |       | 9.11.1   | Clear RAM                                                    | 9-35 |

|    |       |          | RAM Self Test                                                |      |

|    |       | 9.11.3   | ROM Checksum                                                 | 9-36 |

|    |       | 9.11.4   | Binary-to-BCD Conversion                                     |      |

|    |       | 9.11.5   | •                                                            |      |

|    |       | 9.11.6   | BCD String Addition                                          |      |

|    |       | 9.11.7   | Fast Parity                                                  |      |

|    |       | 9.11.8   | Overflow and Underflow                                       |      |

|    |       | 9.11.9   | Bubble Sort                                                  | 9-40 |

|    |       | 9.11.10  | Table Search                                                 | 9-40 |

|    |       | 9.11.11  | 16-Bit Address Stack Operations                              | 9-41 |

|    |       |          | 16-by-16 (32-Bit) Multiplication                             |      |

|    |       | 9.11.13  | Binary Division, Example 1                                   | 9-43 |

|    |       |          | Binary Division, Example 2                                   |      |

|    |       | 9.11.15  | Binary Division, Example 3                                   | 9-44 |

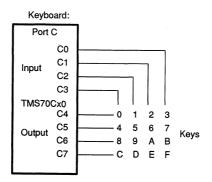

|    |       |          | Keyboard Scan                                                |      |

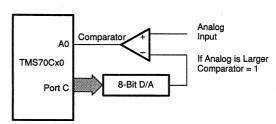

|    |       |          | 8-Bit Analog-to-Digital Converter                            |      |

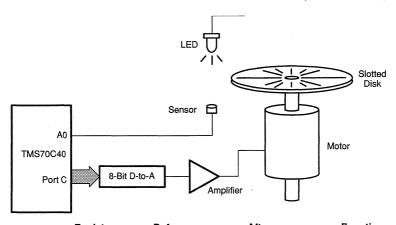

|    |       |          | Motor Speed Controller                                       |      |

|    |       |          |                                                              |      |

| 10 | The T |          | 8-Bit MCU Development Support                                |      |

|    | 10.1  | The RT   | C/EVM7000 Evaluation Module                                  | 10-2 |

|     |       | 10.1.1 Functional Overview                            |        |

|-----|-------|-------------------------------------------------------|--------|

|     |       | 10.1.2 Operating System                               | . 10-3 |

|     | 10.2  | The Interactive Software for the EVM7000              |        |

|     | 100   | 10.2.1 General Information                            |        |

|     | 10.3  | The Extended Development Support                      |        |